30+ data flow modelling in verilog

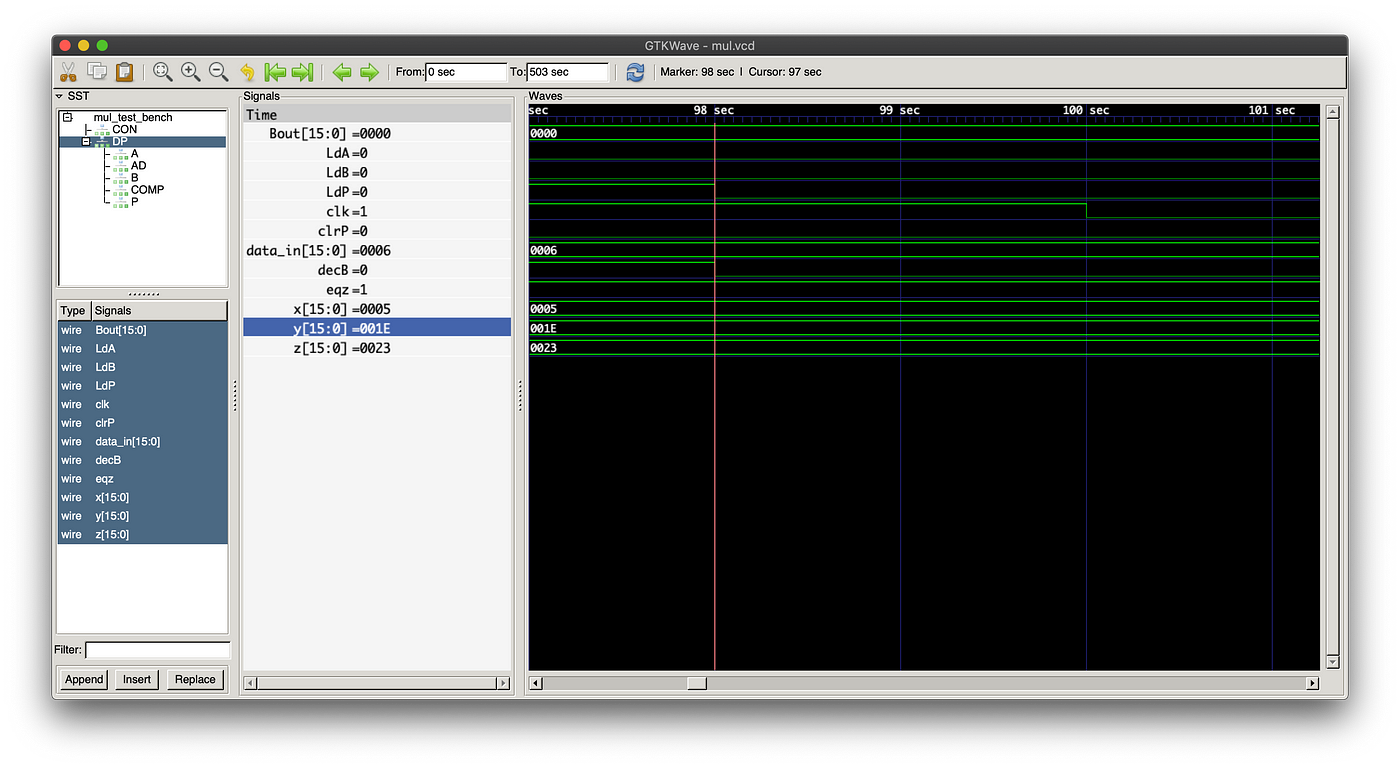

Continuous delivery is a value proposition net. By checking the above waveform we can determine whether our.

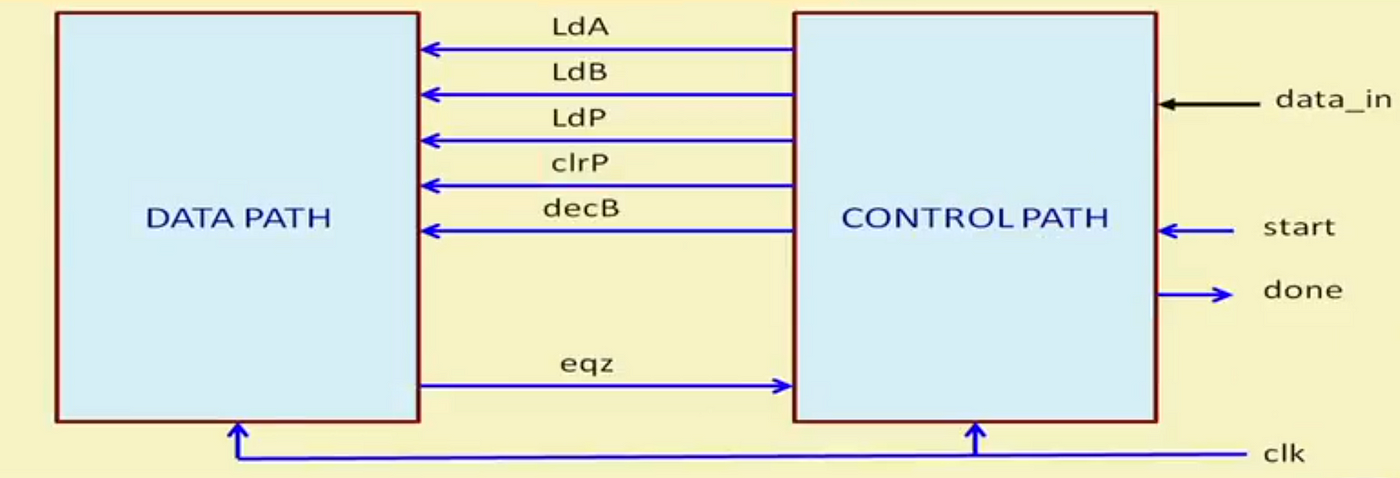

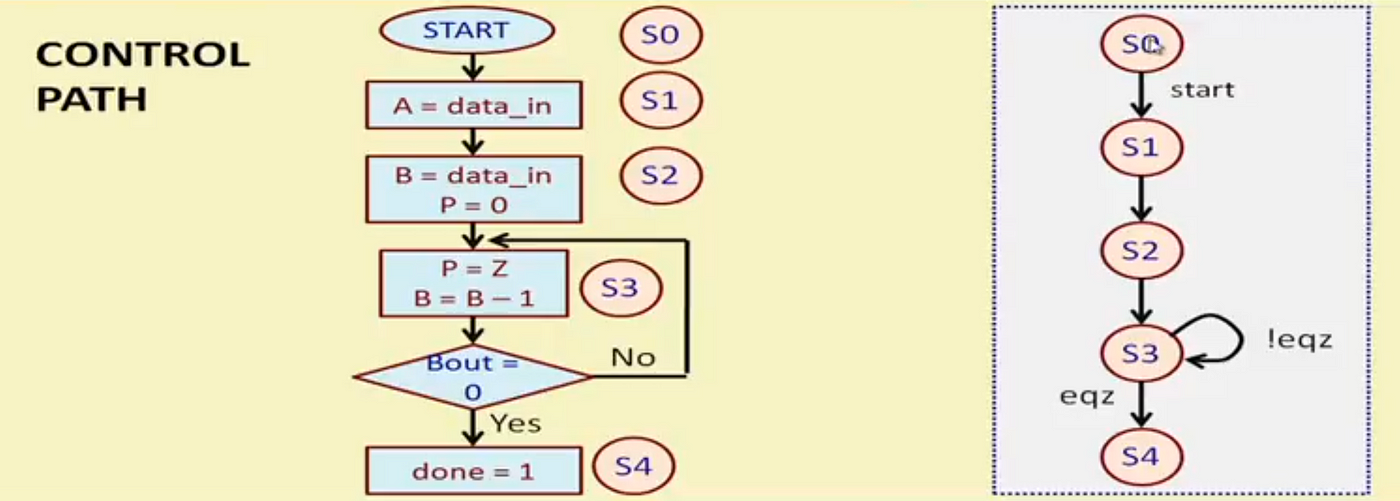

Implementing An Algorithm By Modelling An Fsm In An Hdl By Akshay Anand The Startup Medium

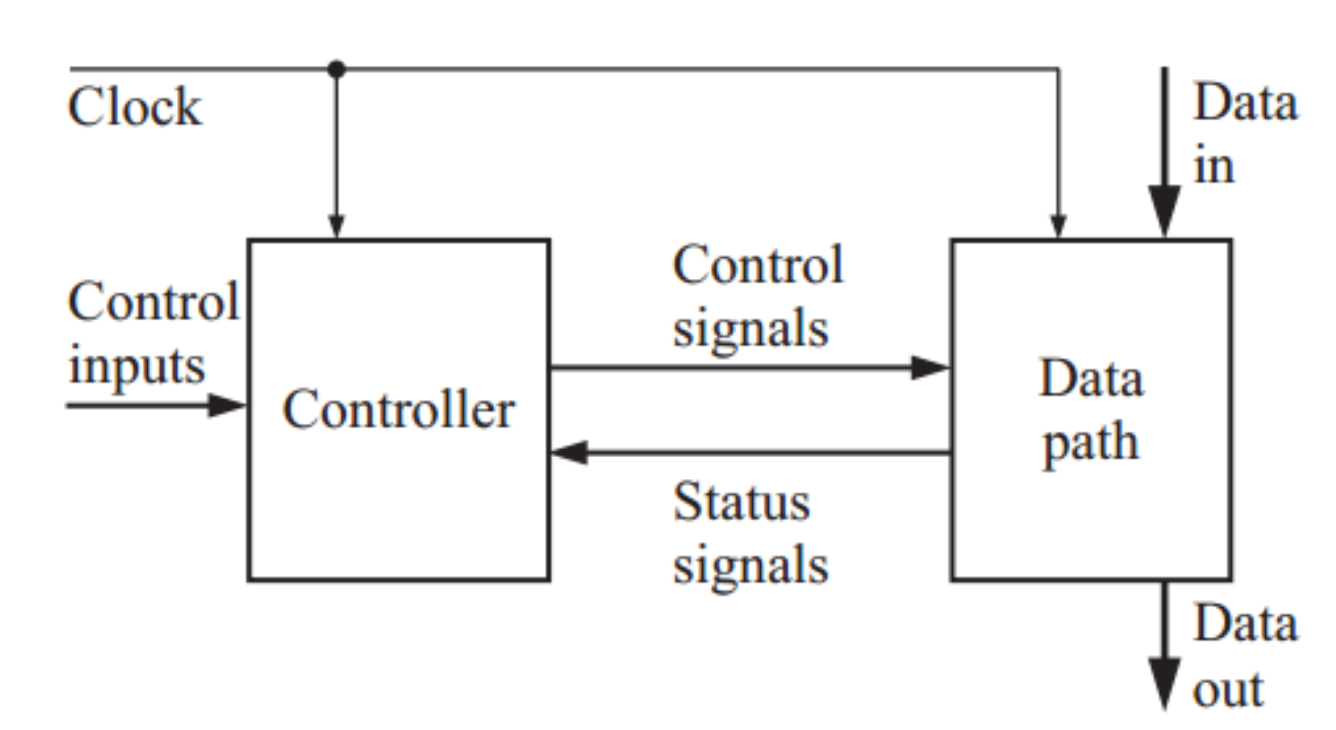

Dataflow modeling uses a number of operators that act on.

. The data network is used in Verilog HDL to. Dataflow modeling provides the means of describing combinational circuits by their function rather than by their gate structure. What is data flow modeling in Verilog.

Verilog provides about 30 operator types. Instead of using directly in data flow we use operations such as Bit-Wise AND Multiply. An example would be the data flow when a processor fetches imaging data from the system ram and executes them.

In this tutorial you will learn the data-flow modeling style of Verilog HDL Hardware Descriptive Language Objectives you will achieve after this tutorial. Dataflow Modeling There are three types of modeling for Verilog. The data flow method allows us to focus on increasing the region by the data flow.

The dataflow modeling style is mainly used to describe. Dataflow modeling describes hardware in terms of the flow of data from input to output. Define expressions operators and.

While the gate-level and dataflow. Dataflow modeling provides the means of describing combinational circuits by their function rather than by their. They are Dataflow Gate-level modeling and behavioral modeling.

Dataflow modeling uses continuous assignments and keyword to share. Behavioral Modelling and Timing. Full Adder in Dataflow model.

Half adder is a combinational arithmetic circuit that adds two numbers and produces a sum bit S and carry bit C as the output. Then we use assignment statements in data flow. In Verilog Behavioral models contain procedural statements which control the simulation and manipulate variables of the data types.

Module fulladder input a input b input cin output s output cout. Verilog full adder in dataflow gate level modelling style. Here we represent Register Transfer Level RTL For OR Gate for both Data Level and Data Flow modelling.

What Is The Difference Between Structural And Behavioural Data Flow Modelling In Verilog Quora

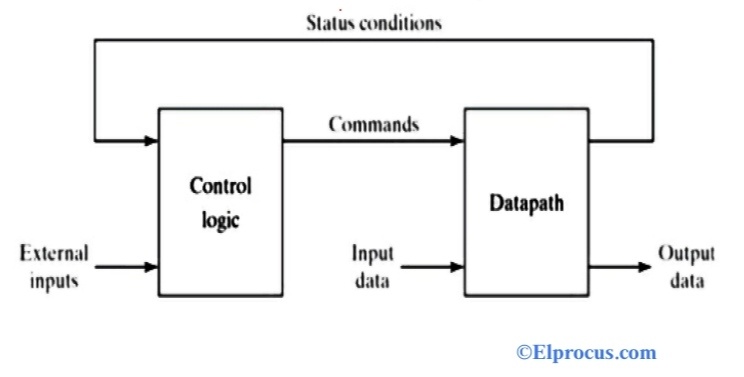

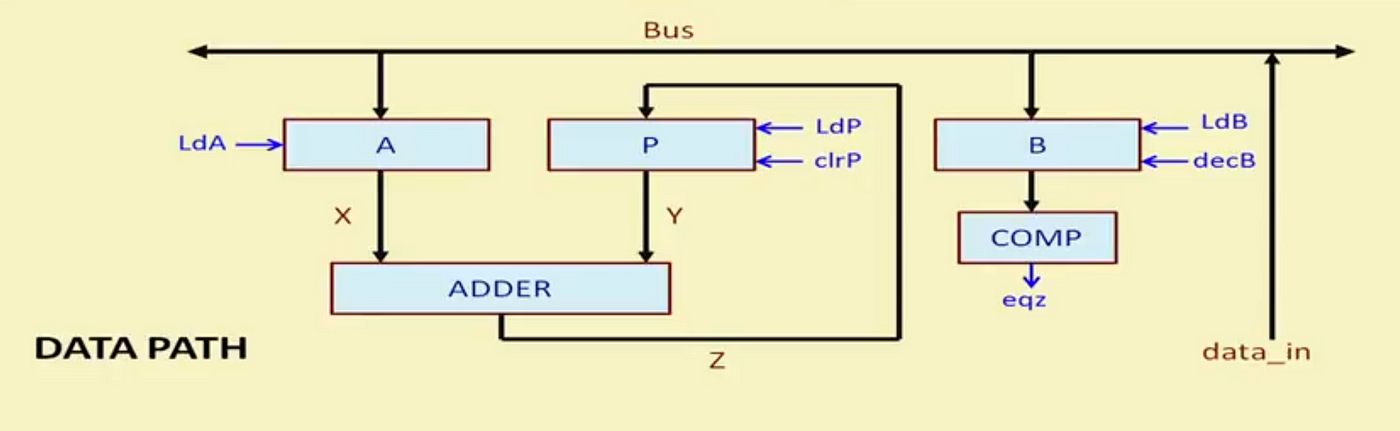

Implementing An Algorithm By Modelling An Fsm In An Hdl By Akshay Anand The Startup Medium

What Is The Difference Between Gate Level Data Flow And Behavioural Modelling In Verilog Quora

What Is The Difference Between Structural And Behavioural Data Flow Modelling In Verilog Quora

Implementing An Algorithm By Modelling An Fsm In An Hdl By Akshay Anand The Startup Medium

What Is The Difference Between Gate Level Data Flow And Behavioural Modelling In Verilog Quora

What Is The Difference Between Structural And Behavioural Data Flow Modelling In Verilog Quora

What Is The Difference Between Structural And Behavioural Data Flow Modelling In Verilog Quora

What Is The Difference Between Structural And Behavioural Data Flow Modelling In Verilog Quora

Implementing An Algorithm By Modelling An Fsm In An Hdl By Akshay Anand The Startup Medium

Digital Design Expert Advise 2021

What Is The Difference Between Gate Level Data Flow And Behavioural Modelling In Verilog Quora

The Growing Uncertainty Of Sign Off At 7 5nm

What Is The Difference Between Gate Level Data Flow And Behavioural Modelling In Verilog Quora

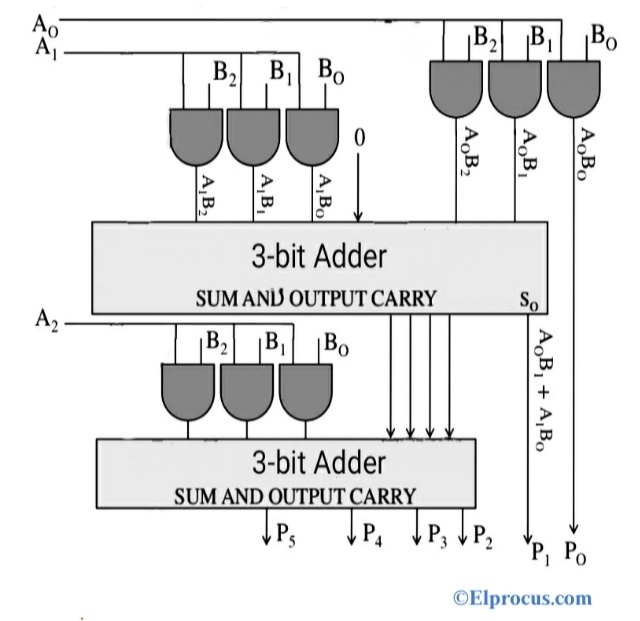

Binary Multiplier Types Block Diagram Working And Its Applications

Binary Multiplier Types Block Diagram Working And Its Applications

Implementing An Algorithm By Modelling An Fsm In An Hdl By Akshay Anand The Startup Medium